If you are interested please let me know so i can provide more details. Click on Library menu from the main window and then click on the plus sign next to the work library.

Alu Design In Verilog With Text Bench Youtube

Xilinx ISE 4 Bit ALU Add Subtract - Verilog.

. You may use ModelSim or Xilinx to code your Verilog programs. 4-bit ALU using VHDL By Mohd Kashif Contributed Content Thursday August 29 2013 The project is a 4-bit ALU in VHDL with a total of 16 operations which includes various. ALU Arithmetic Logic Unit is a digital circuit which does arithmetic and logical operations.

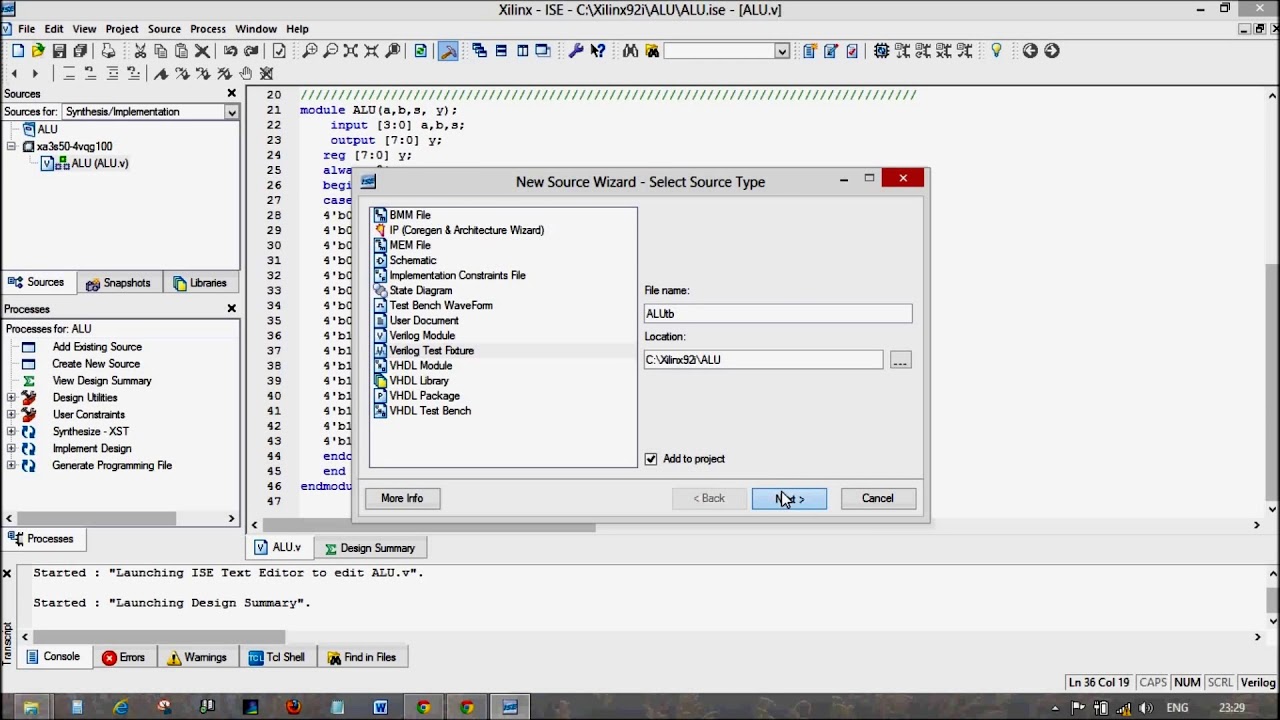

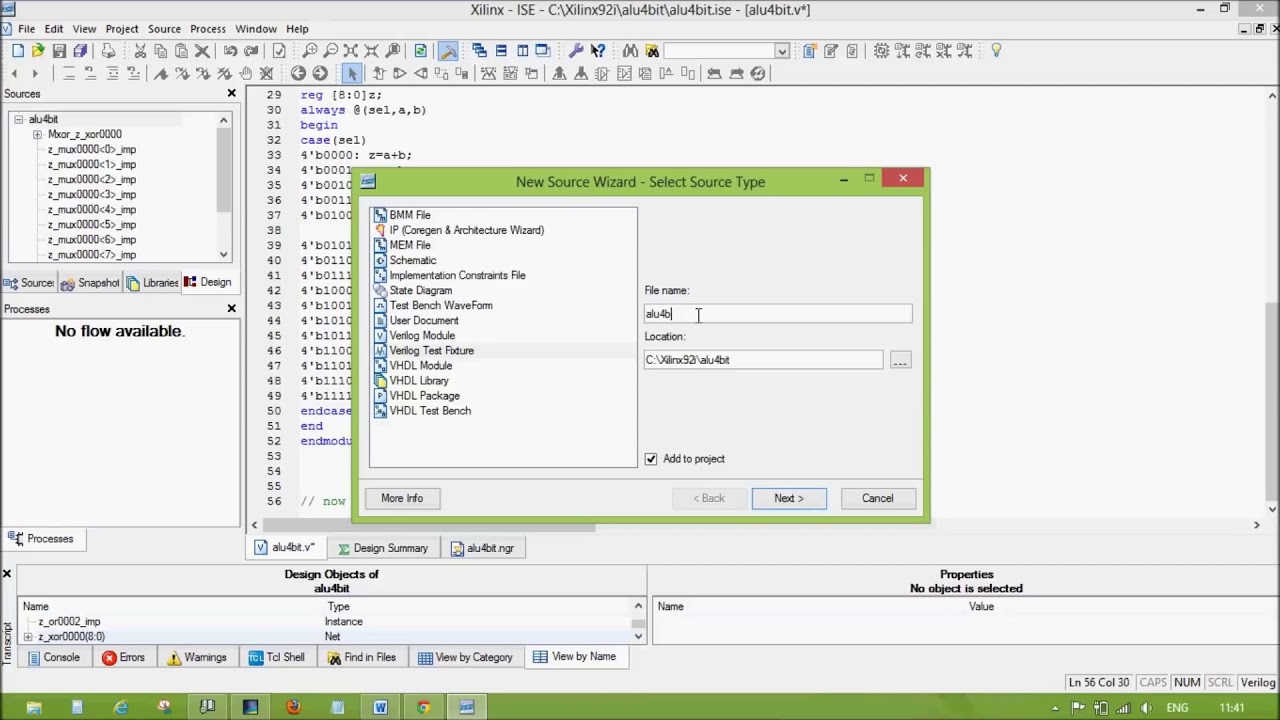

Simulating the ALU design 1. You should see the name Top_ALU code that. I want to create a 4 bit ALU that can add and divide and do other operation using Xilinx ISE design suite 147.

USF-XSim-97 XSim simulation ran for 1000ns. On the other hand when M1 the output of the 4-bit ALU is a 2s. Full VHDL code for the ALU was presented.

We have explored the ALU. Most of the ALUs used in practical designs are far more. Hi all I am trying to implement a 4 bit ALU using structural VHDL programming.

There are 6 different functions implemented in this ALU. Input 30 a b. 4 Bit ALU using Verilog.

If you followed all above steps then you have successfuly learned Xilinx to simulate Verilog programs. Design methodology has been changing from schematic design to HDL based design. 35 Dislike Share Save.

Its a basic block in. Note that this is one of the simplest architecture of an ALU. Contribute to GajjarMihir4---bit-ALU development by creating an account on GitHub.

Last time I introduced the N-bit adder design in Verilog which is a part of a 16-bit ALU design I will present todayThe 16-bit ALU is a core combinational component of the. I am using 161 mux for operation selection on the inputs of ALU. Design snapshot alu_behav loaded.

Output reg 70 y. Verilog code for 4 bit ALU Design. Here verilog HDL was coded using Quartus II 90 version software and 4 bit ALU hardware design was done using Proteus software.

4 bit ALU Design in verilog using Xilinx Simulator 21336 views Jan 19 2018 150 Dislike Share Save 2Dix Inc 500 subscribers Subscribe In this Video you will learn how to design or implement the 4. This 161 is again an 41 which breaks down. Verilog code for Arithmetic Logic Unit ALU Last time an Arithmetic Logic Unit ALU is designed and implemented in VHDL.

Part 1 Final ALU Design. This is a 4 bit ALU that Adds and Substract4 Bit Full Adder -httpsyoutubeDVkbizPyde4. It has both Structural as well as Behavioral models.

Mihir Gajjar and Mihir Gajjar 4 - bit ALU using Verilog. 4 bit ALU-Verilog Code By Its Fun Blog - June 08 2015 Hi Friends I come up with a new post on 4 bit ALU using Verilog. We have earlier seen how we have used delays when creating a testbench C-in C-out hence overflow 1-bit ALU - overflow 1 0 Stars 109 Views Author.

1 BIT ALU Design Complete Structure of ALU Verilog Code timescale 1ns 1ps module ALUinput 310ainput 310binput 20foutput 310resultoutput zeroflagoutput. This paper presents design concept of 4-bit arithmetic and logic unit ALU. Timescale 1ns 1ps.

In this article I have shared Verilog code for a simple ALU. Module alu a b sel en y. Verilog code for arithmetic logic unit alu 4 bit alu design in verilog using xilinx simulator verilog tutorial department of electrical and computer verilog amp fpga fundamentals eight bit alu.

4-bit ALU Design. Simulation Result for 4-bit ALU ALU ALUs comprise the combinational logic that implements logic operations such as AND OR NOT gate and arithmetic operations such as. 4 bit ALU Design in verilog using Xilinx.

Cpu 000003.

Lesson 60 Example 36 4 Bit Arithmetic Logic Unit Alu Youtube

Xilinx Ise 4 Bit Alu Add Subtract Verilog Youtube

Xilinx Ise Full Adder 4 Bit Verilog Youtube

4 Bit Alu Design In Verilog Using Xilinx Simulator Youtube

Alu Design In Verilog With Testbench Simulation In Modelsim Arithmetic Logic Unit Youtube

0 comments

Post a Comment